# Algèbre de Boole

# Série Complète d'Apprentissage

De la Théorie aux Applications Pratiques

10 Fiches Pédagogiques

Pour Radioamateurs et Passionnés d'Électronique

73 de F4HXN

https://f4hxn.fr

# **Table des Matières**

FICHE 1 : Le Système Binaire

Conversions, arithmétique, complément à 2

FICHE 2 : Les Bases de l'Algèbre de Boole

Opérations logiques, lois fondamentales, théorèmes

FICHE 3: Portes Logiques et Circuits

Symboles, caractéristiques, familles TTL et CMOS

FICHE 4 : Systèmes de Numération

Octal, hexadécimal, BCD, code Gray

FICHE 5 : Tableaux de Karnaugh

Simplification graphique des circuits logiques

FICHE 6: Circuits Combinatoires

Additionneurs, multiplexeurs, décodeurs, ALU

FICHE 7 : Circuits Séquentiels et Mémoires

Bascules, registres, compteurs, RAM/ROM

#### FICHE 8 : Machines à États Finis

FSM de Moore et Mealy, diagrammes d'états

## FICHE 9 : Applications en Radio Amateur

CTCSS, DCS, relais, DTMF, modes numériques

#### **FICHE 10 :** Programmation et Logique

Opérateurs bit à bit, FPGA, VHDL, simulation

FICHE 1

# Le Système Binaire

Comprendre le langage fondamental des ordinateurs et de l'électronique numérique

# **Qu'est-ce que le Système Binaire?**

Le système binaire est un système de numération en base 2, utilisant uniquement deux chiffres : 0 et 1. C'est le système naturel de l'électronique numérique, où un signal électrique peut être soit présent (1) soit absent (0).

#### Pourquoi le binaire ?

L'électronique numérique utilise le binaire car il est facile de distinguer deux états électriques (tension haute/basse) avec une grande fiabilité, même en présence de bruit. Contrairement au système décimal (base 10) que nous utilisons quotidiennement, le binaire est parfaitement adapté au fonctionnement physique des circuits électroniques.

#### Comparaison des systèmes

- Système décimal (base 10): utilise 10 chiffres (0, 1, 2, 3, 4, 5, 6, 7, 8,

- Système binaire (base 2) : utilise 2 chiffres (0, 1)

- Système octal (base 8) : utilise 8 chiffres (0 à 7)

- Système hexadécimal (base 16) : utilise 16 symboles (0 à 9, A à F)

## Le Bit : Unité Fondamentale

Le **bit** (contraction de "binary digit") est la plus petite unité d'information en informatique. Un bit peut prendre la valeur 0 ou 1.

#### Niérarchie des unités :

- 1 bit = une valeur binaire (0 ou 1)

- 1 **nibble** = 4 bits

- 1 octet (byte) = 8 bits

- 1 mot (word) = 16, 32 ou 64 bits selon l'architecture

## Capacité de représentation

Avec **n bits**, on peut représenter **2**<sup>n</sup> **valeurs différentes** :

| Nombre de<br>bits | Valeurs possibles                   | Plage (0 à)          |

|-------------------|-------------------------------------|----------------------|

| 1 bit             | 21 = 2                              | 0 à 1                |

| 2 bits            | 22 = 4                              | 0 à 3                |

| 3 bits            | 23 = 8                              | 0 à 7                |

| 4 bits            | 24 = 16                             | 0 à 15               |

| 8 bits            | 28 = 256                            | 0 à 255              |

| 16 bits           | 216 = 65 536                        | 0 à 65 535           |

| 32 bits           | 2 <sup>3 2</sup> = 4 294 967<br>296 | 0 à 4 294 967<br>295 |

# **Conversion Binaire** $\leftrightarrow$ **Décimal**

# Table de correspondance (0 à 15)

| Décimal | Binaire (4 bits) | Décimal | Binaire (4 bits) |

|---------|------------------|---------|------------------|

| 0       | 0000             | 8       | 1000             |

| 1       | 0001             | 9       | 1001             |

| 2       | 0010             | 10      | 1010             |

| 3       | 0011             | 11      | 1011             |

| 4       | 0100             | 12      | 1100             |

| 5       | 0101             | 13      | 1101             |

| 6       | 0110             | 14      | 1110             |

| 7       | 0111             | 15      | 1111             |

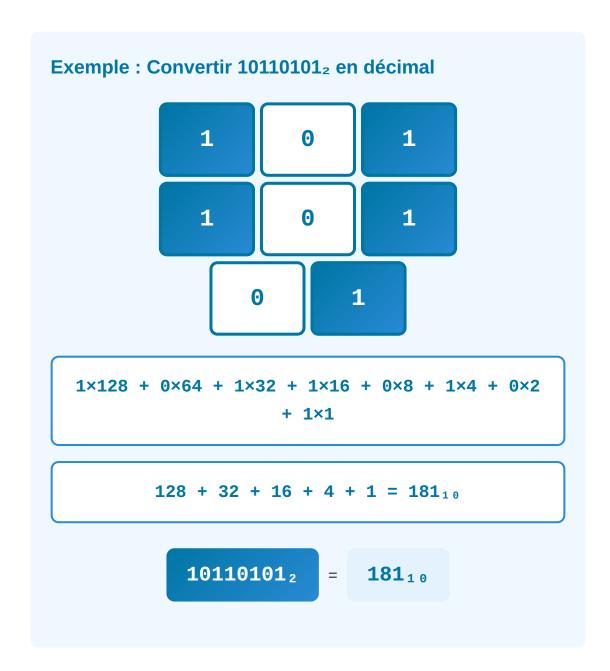

## **Du Binaire vers le Décimal**

Chaque position dans un nombre binaire représente une puissance de 2 :

|     |    |    |    | 23 |   |   |   |

|-----|----|----|----|----|---|---|---|

| 128 | 64 | 32 | 16 | 8  | 4 | 2 | 1 |

#### Du Décimal vers le Binaire

Pour convertir un nombre décimal en binaire, on utilise la **méthode des divisions successives par 2** :

## **Exemple:** Convertir 45<sub>10</sub> en binaire

- 1  $45 \div 2 = 22 \text{ reste } 1 \leftarrow \text{ bit de poids faible (LSB)}$

- 22 ÷ 2 = 11 reste **0**

- 3  $11 \div 2 = 5 \text{ reste } 1$

- 4  $5 \div 2 = 2 \text{ reste } 1$

- 5 2 ÷ 2 = 1 reste **0**

- 6  $1 \div 2 = 0$  reste 1  $\leftarrow$  bit de poids fort (MSB)

On lit les restes de bas en haut :

1011012

# **Opérations Arithmétiques en Binaire**

#### **Addition Binaire**

```

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10 (0 avec retenue de 1)

```

#### **Exemple:**

```

1011 (11)

+ 110 (6)

-----

10001 (17)

```

#### **Soustraction Binaire**

```

0 - 0 = 0

1 - 0 = 1

1 - 1 = 0

10 - 1 = 1 (avec emprunt)

```

#### Exemple:

```

1101 (13)

- 101 (5)

-----

1000 (8)

```

# **Multiplication Binaire**

#### Exemple:

```

101 (5)

× 11 (3)

----

101

+ 101

----

1111 (15)

```

#### **Division Binaire**

Similaire à la division décimale, mais avec les règles binaires.

# **Applications Pratiques**

#### **En Radio Amateur**

#### Codes de sous-tonalités CTCSS

Les fréquences CTCSS sont souvent programmées en binaire dans les transceiveurs numériques. Par exemple, la fréquence 88.5 Hz pourrait être codée sur 8 bits.

#### **Modes numériques**

Les modes comme **FT8**, **WSPR**, **PSK31** transmettent des données binaires. Chaque caractère est converti en binaire avant la transmission.

#### Adressage mémoire

Les canaux mémoire d'un transceiver sont numérotés en binaire en interne. Un appareil avec 100 mémoires utilise 7 bits ( $2^7 = 128$  positions).

# **En Informatique**

#### Représentation des données :

- Texte : Chaque caractère est codé en binaire (ASCII, Unicode)

- **Images :** Chaque pixel est représenté par des valeurs binaires (RGB)

- Son : L'amplitude du signal est échantillonnée et convertie en binaire

- Instructions processeur : Chaque instruction machine est un code binaire

# Masques et Opérations Bit à Bit

Les opérations bit à bit permettent de manipuler des bits individuels :

## **Décalages (Shifts)**

Décalage à gauche (Left Shift) : nombre × 2

00101101 << 1 = 01011010

Équivalent à multiplier par 2

#### Décalage à droite (Right Shift) : nombre ÷ 2

00101100 >> 1 = 00010110

Équivalent à diviser par 2

# Masquage de bits

## Extraire un bit spécifique

Pour lire le bit 3 d'un octet :

Valeur : 10110101

Masque :  $00001000 (2^3)$

Résultat AND :  $00000000 \rightarrow bit = 0$

#### Mettre un bit à 1

Pour activer le bit 5 :

Valeur : 10010101

Masque : 00100000 (2<sup>5</sup>)

**Résultat OR : 10110101**

# **Exercices Pratiques**

#### **Exercice 1: Conversion**

Convertir en décimal:

- 11010<sub>2</sub> = ?

- $101011_2 = ?$

- 11111111<sub>2</sub> = ?

#### **Voir les réponses**

- $11010_2 = 26_{10}$

- $101011_2 = 43_{10}$

- $11111111_2 = 255_{10}$

#### **Exercice 2: Addition**

Calculer:

- $1010_2 + 0111_2 = ?$

- $1101_2 + 1011_2 = ?$

#### Voir les réponses

- $1010_2 + 0111_2 = 10001_2 (10 + 7 = 17)$

- $1101_2 + 1011_2 = 11000_2$  (13 + 11 = 24)

#### Exercice 3 : Puissances de 2

Combien de valeurs peut-on représenter avec :

- 5 bits ?

- 12 bits ?

- 20 bits ?

#### Voir les réponses

• 5 bits :  $2^5$  = 32 valeurs (0 à 31)

• 12 bits :  $2^{12} = 4096$  valeurs

• 20 bits : 2<sup>20</sup> = 1 048 576 valeurs

## Points Clés à Retenir

- Le binaire utilise uniquement 0 et 1

- Chaque position représente une puissance de 2

- Avec n bits, on peut représenter 2<sup>n</sup> valeurs

- L'addition binaire suit des règles simples avec retenues

- Les décalages multiplient ou divisent par 2

- Le binaire est le langage natif de tous les circuits numériques

73 de F4HXN - Prochaine fiche : L'algèbre de Boole ! 📡

FICHE 2

# Les Bases de l'Algèbre de Boole

Découvrez les fondements mathématiques de l'électronique numérique et de l'informatique moderne

# Introduction à l'Algèbre de Boole

L'algèbre de Boole, développée par le mathématicien britannique **George Boole** en 1854, est un système algébrique qui manipule des valeurs binaires.

Cette algèbre est aujourd'hui fondamentale pour l'électronique numérique,

l'informatique et les télécommunications.

Principe fondamental: En algèbre de Boole, les variables ne peuvent prendre que deux valeurs possibles: 0 (FAUX) ou 1 (VRAI).

Ces deux états peuvent représenter :

• En logique : Vrai / Faux

• En électronique : Tension haute / Tension basse

• En informatique : Bit à 1 / Bit à 0

• En radio amateur : Signal présent / Signal absent

# Les Opérations de Base

## 1. L'opération ET (AND) - Conjonction

L'opération ET retourne **VRAI (1)** uniquement si **toutes** les entrées sont vraies.

#### A · B ou A A B ou A AND B

| А | В | A · B |

|---|---|-------|

| 0 | Θ | Θ     |

| 0 | 1 | Θ     |

| 1 | 0 | Θ     |

| 1 | 1 | 1     |

#### **Exemple radio amateur**

Un relais ne s'active que si le signal CTCSS est correct **ET** que la porteuse est présente.

## 2. L'opération OU (OR) - Disjonction

L'opération OU retourne VRAI (1) si au moins une des entrées est vraie.

A + B ou A V B ou A OR B

| А | В | A + B |

|---|---|-------|

| 0 | 0 | Θ     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 1     |

## **Exemple radio amateur**

Une alarme se déclenche si la température est trop élevée **OU** si la tension d'alimentation est trop faible.

# 3. L'opération NON (NOT) - Négation

L'opération NON inverse la valeur de l'entrée.

Ā ou ¬A ou NOT A

| А | Ā |

|---|---|

| Θ | 1 |

| 1 | 0 |

#### **Exemple radio amateur**

Un système de coupure coupe l'émetteur (sortie à 0) quand l'interrupteur PTT est **NON** activé.

# **Les Opérations Composées**

## 4. L'opération NON-ET (NAND)

L'opération NAND est l'inverse du ET. C'est une opération **universelle** : on peut créer toutes les autres portes logiques uniquement avec des NAND.

$$A NAND B = A \cdot B$$

| Α | В | A NAND B |

|---|---|----------|

| 0 | Θ | 1        |

| 0 | 1 | 1        |

| 1 | 0 | 1        |

| 1 | 1 | Θ        |

## 5. L'opération NON-OU (NOR)

L'opération NOR est l'inverse du OU. C'est également une opération universelle.

#### A NOR B = A + B

| А | В | A NOR B |

|---|---|---------|

| 0 | 0 | 1       |

| Θ | 1 | Θ       |

| 1 | 0 | Θ       |

| 1 | 1 | 0       |

# 6. L'opération OU Exclusif (XOR)

L'opération XOR retourne VRAI si les entrées sont **différentes**.

#### A ⊕ B ou A XOR B

| Α | В | A ⊕ B |

|---|---|-------|

| 0 | 0 | Θ     |

| 0 | 1 | 1     |

| 1 | Θ | 1     |

| 1 | 1 | Θ     |

#### Utilisation en cryptographie

Le XOR est fondamental en cryptographie pour chiffrer/déchiffrer des données, car  $A \oplus B \oplus B = A$

# Les Lois de l'Algèbre de Boole

#### Lois de commutativité

$$A \cdot B = B \cdot A$$

$$A + B = B + A$$

#### Lois d'associativité

$$A \cdot (B \cdot C) = (A \cdot B) \cdot C$$

$$A + (B + C) = (A + B) + C$$

#### Lois de distributivité

$$A \cdot (B + C) = (A \cdot B) + (A \cdot C)$$

$$A + (B \cdot C) = (A + B) \cdot (A + C)$$

#### Lois d'identité

$$A \cdot 1 = A$$

$$A + 0 = A$$

# Lois de complémentation

$$A \cdot \bar{A} = 0$$

$$A + \bar{A} = 1$$

# Lois de De Morgan

Très importantes! Ces lois permettent de transformer les expressions logiques.

$$A \cdot B = \bar{A} + \bar{B}$$

$$A + B = \bar{A} \cdot \bar{B}$$

# Applications Pratiques

#### **Processeurs**

Tous les calculs dans un processeur sont effectués par des milliards de portes logiques.

#### Circuits intégrés

Les circuits CMOS utilisent l'algèbre de Boole pour créer des fonctions complexes.

#### **Télécommunications**

Encodage, décodage, et correction d'erreurs dans les transmissions numériques.

#### Intelligence artificielle

Les réseaux de neurones artificiels utilisent des opérations logiques.

#### Radio numérique

Modes numériques (FT8, WSPR, etc.) basés sur le traitement logique des signaux.

#### **Sécurité**

Algorithmes de chiffrement et de hachage utilisent intensivement le XOR.

# **Exemple Pratique : Circuit de Sécurité**

Imaginons un système de sécurité pour un émetteur radio qui doit respecter les conditions suivantes :

#### Cahier des charges :

- L'émetteur peut fonctionner SI l'alimentation est OK **ET** la température est normale

- Une alarme sonne SI la température est élevée OU si le ROS est mauvais

- Le ventilateur s'active SI l'émetteur fonctionne ET que la puissance > 50W

#### **Variables**

- A = Alimentation OK (1) ou KO (0)

- T = Température normale (1) ou élevée (0)

- R = ROS bon (1) ou mauvais (0)

- **P** = Puissance > 50W (1) ou  $\leq$  50W (0)

# **Équations logiques**

Émission =

$$A \cdot T$$

Alarme =

$$\bar{T} + \bar{R}$$

Ventilateur = Émission

$$\cdot$$

P = A  $\cdot$  T  $\cdot$  P

#### **Simplification**

Grâce aux lois de De Morgan, on peut simplifier :

Alarme =

$$\bar{T} + \bar{R} = T \cdot R$$

Ce qui signifie : "L'alarme sonne si ce n'est PAS le cas que (température ET ROS sont bons)"

# **Conclusion**

L'algèbre de Boole est un outil mathématique puissant et élégant qui constitue la base de toute l'électronique numérique moderne. Sa simplicité apparente cache une grande richesse et permet de concevoir des systèmes extrêmement complexes.

Pour aller plus loin : L'algèbre de Boole s'étend à des concepts plus avancés comme les tableaux de Karnaugh pour la simplification de circuits, les bascules et les mémoires, et les machines à états finis utilisées dans les protocoles de communication numérique.

73 de F4HXN - Prochaine fiche : Les portes logiques ! 📡

FICHE 3

# Les Portes Logiques et **Circuits**

Découvrez les composants électroniques qui réalisent les opérations booléennes

# **Qu'est-ce qu'une Porte Logique?**

Une **porte logique** est un circuit électronique qui réalise une opération booléenne. Elle possède une ou plusieurs entrées et une sortie dont l'état dépend des états des entrées selon une fonction logique définie.

#### Principe de fonctionnement :

Les portes logiques sont constituées de transistors qui agissent comme des interrupteurs électroniques. Un transistor peut être dans deux états : passant (1) ou bloqué (0). En combinant plusieurs transistors, on crée des fonctions logiques complexes.

# Représentation des portes logiques

Il existe deux normes principales pour représenter les portes logiques :

- Norme américaine (ANSI/MIL) : utilise des formes géométriques distinctives

- Norme européenne (IEC) : utilise des rectangles avec des symboles

Dans cette fiche, nous utiliserons principalement la norme américaine, plus répandue en électronique amateur.

# **Les Portes Logiques Fondamentales**

## 1. Porte NON (NOT / Inverseur)

Symbole: Porte NON

Fonction: Inverse l'état de l'entrée

**Équation**: Sortie =  $\bar{A}$

## 2. Porte ET (AND)

Symbole : Porte ET

Fonction : Sortie à 1 si TOUTES les entrées sont à 1

**Équation**: Sortie =  $A \cdot B$

# 3. Porte OU (OR)

Symbole: Porte OU

Fonction: Sortie à 1 si AU MOINS UNE entrée est à 1

**Équation :** Sortie = A + B

#### 4. Porte NON-ET (NAND)

**Fonction :** ET suivi d'une inversion (porte universelle)

**Équation**: Sortie =  $A \cdot B$

Porte universelle: La NAND est dite "universelle" car on peut créer toutes les autres portes logiques uniquement avec des NAND. C'est la raison pour laquelle le circuit intégré 7400 (quad NAND) est l'un des plus utilisés.

#### 5. Porte NON-OU (NOR)

**Fonction**: OU suivi d'une inversion (porte universelle)

**Équation :** Sortie = A + B

## 6. Porte OU Exclusif (XOR)

Fonction : Sortie à 1 si les entrées sont DIFFÉRENTES

**Équation**: Sortie = A ⊕ B

#### Application pratique : Détecteur de changement

Une porte XOR peut détecter si deux signaux sont différents. En radio amateur, on peut l'utiliser pour comparer un signal reçu avec un signal de référence et détecter les variations.

# **Tableau Récapitulatif des Portes**

| Porte | Symbole                  | Équation | Sortie = 1 si        |

|-------|--------------------------|----------|----------------------|

| NOT   | Triangle + cercle        | Ā        | A = 0                |

| AND   | Forme D                  | A · B    | A = 1 ET B = 1       |

| OR    | Forme bouclier           | A + B    | A = 1 OU B = 1       |

| NAND  | AND + cercle             | A·B      | PAS (A = 1 ET B = 1) |

| NOR   | OR + cercle              | A + B    | A = 0 ET B = 0       |

| XOR   | OR avec double<br>entrée | A⊕B      | A≠B                  |

# **Familles Logiques**

Les portes logiques sont fabriquées selon différentes technologies, appelées **familles logiques**. Chaque famille a ses propres caractéristiques de vitesse, consommation et niveaux de tension.

# **Principales familles**

#### TTL

#### Transistor-Transistor Logic

| Tension : | 5V      |

|-----------|---------|

| Vitesse:  | Moyenne |

| Conso:    | Élevée  |

#### **CMOS**

#### Complementary MOS

| Tension: | 3-15V       |

|----------|-------------|

| Vitesse: | Variable    |

| Conso:   | Très faible |

#### **74HC**

#### High-Speed CMOS

| Tension: | 2-6V   |

|----------|--------|

| Vitesse: | Rapide |

| Conso:   | Faible |

#### **74LS**

#### Low-Power Schottky

| Tension : | 5V      |

|-----------|---------|

| Vitesse:  | Rapide  |

| Conso:    | Moyenne |

#### **©** Choix de la famille :

- 74HC: Excellent choix pour la plupart des projets amateurs (faible consommation, bonne vitesse)

- **74LS** : Pour compatibilité avec circuits anciens

- CMOS 4000 : Pour très faible consommation (batteries)

- 74AC/ACT : Pour applications haute fréquence

# **Circuits Intégrés Classiques**

Les portes logiques sont regroupées dans des **circuits intégrés** (CI ou IC en anglais). Voici les plus courants en format DIP (Dual In-line Package) à 14 ou 16 broches :

# 7400 Quad NAND

#### 4 portes NAND à 2 entrées

La porte universelle par excellence. Indispensable pour tout projet de logique combinatoire.

# 7402 Quad NOR

#### 4 portes NOR à 2 entrées

Autre porte universelle, très utile pour certains montages.

# 7404 Hex NOT

#### 6 inverseurs

Pour inverser des signaux logiques.

# 7408 Quad AND

#### 4 portes AND à 2 entrées

Pour fonctions ET simples.

# 7432 Quad OR

4 portes OR à 2 entrées

Pour fonctions OU simples.

# 7486 Quad XOR

4 portes XOR à 2 entrées

Comparateurs, détecteurs de parité.

# 7410 Triple NAND-3

3 portes NAND à 3 entrées

Quand plus de 2 entrées sont nécessaires.

# 7411 Triple AND-3

3 portes AND à 3 entrées

ET à 3 entrées.

- Attention : Les circuits intégrés logiques nécessitent :

- Condensateur de découplage (100nF) entre Vcc et GND, proche du CI

- Respect strict de la polarité d'alimentation

- Ne jamais laisser d'entrée CMOS "en l'air" (flottante)

- Protection contre les décharges électrostatiques (ESD) pour les CMOS

# Caractéristiques Électriques Importantes

### 1. Fan-out (Facteur de charge)

Le **fan-out** est le nombre maximal d'entrées qu'une sortie peut piloter sans dégrader le signal.

### **Exemple**

Un 7400 TTL a un fan-out de 10 : une sortie peut piloter jusqu'à 10 entrées TTL standard.

Un 74HC00 CMOS peut théoriquement piloter des centaines d'entrées (très haute impédance d'entrée).

### 2. Temps de Propagation

Le **temps de propagation** (t<sub>pd</sub>) est le délai entre un changement d'entrée et la réponse de la sortie.

| Famille   | Temps de propagation | Fréquence max |

|-----------|----------------------|---------------|

| 74LS      | ~10 ns               | ~25 MHz       |

| 74HC      | ~8 ns                | ~30 MHz       |

| 74AC      | ~4 ns                | ~100 MHz      |

| CMOS 4000 | ~60 ns               | ~5 MHz        |

# 3. Niveaux Logiques

Les niveaux de tension définissant les états logiques varient selon la famille :

#### Pour TTL 5V:

• Niveau BAS (0): 0V à 0.8V

• Niveau HAUT (1): 2V à 5V

• Zone interdite: 0.8V à 2V

#### Pour CMOS 5V:

• Niveau BAS (0) : 0V à 1.5V

• Niveau HAUT (1): 3.5V à 5V

• Zone interdite : 1.5V à 3.5V

# Lire une Datasheet (Fiche Technique)

La **datasheet** est le document indispensable pour utiliser correctement un circuit intégré. Voici les sections importantes :

#### Sections essentielles d'une datasheet

### 1. Description générale

- Type de circuit (quad NAND, etc.)

- Famille logique (TTL, CMOS, etc.)

- Boîtier disponible (DIP, SOIC, etc.)

### 2. Brochage (Pin Configuration)

- Numéro et fonction de chaque broche

- Repère de la broche 1 (encoche ou point)

- Broches d'alimentation (Vcc et GND)

### 3. Caractéristiques électriques maximales

- Tension d'alimentation (min/typ/max)

- Courant de sortie maximal

- Puissance dissipée maximale

- Température de fonctionnement

#### 4. Caractéristiques de fonctionnement

- Niveaux logiques (VIL, VIH, VOL, VOH)

- Temps de propagation

- Consommation électrique

#### 5. Table de vérité

Comportement logique du circuit

### **Q** Où trouver les datasheets ?

- Site du fabricant (Texas Instruments, NXP, etc.)

- Distributeurs (Mouser, Digi-Key, Farnell)

- AllDataSheet.com

- DatasheetCatalog.com

# **Projet Pratique: Circuit Simple**

### Réaliser un OU Exclusif avec des NAND

Objectif : construire une fonction XOR uniquement avec des portes NAND (démonstration de la porte universelle).

### Matériel nécessaire

- 1× Circuit intégré 7400 (quad NAND) ou 74HC00

- 1× Plaque d'essai (breadboard)

- 2× Interrupteurs ou boutons poussoirs

- 1× LED + résistance 330Ω

- Alimentation 5V

- Fils de connexion

- Condensateur 100nF (découplage)

# **Équation XOR avec NAND**

$$\mathsf{A} \oplus \mathsf{B} = (\mathsf{A} \cdot (\mathsf{A} \cdot \mathsf{B})) \cdot (\mathsf{B} \cdot (\mathsf{A} \cdot \mathsf{B}))$$

Il faut 4 portes NAND pour réaliser un XOR.

### Étapes:

- 1. NAND1: calculer A · B

- 2. NAND2 : calculer A · (sortie NAND1)

- 3. NAND3 : calculer B · (sortie NAND1)

- 4. NAND4 : calculer (sortie NAND2) · (sortie NAND3)

### **Vérification:**

Testez toutes les combinaisons d'entrées :

- A=0, B=0 → LED éteinte (0)

- A=0, B=1 → LED allumée (1)

- A=1, B=0 → LED allumée (1)

- A=1, B=1 → LED éteinte (0)

C'est bien le comportement d'un XOR! ✓

# **Applications en Radio Amateur**

# 1. Séquenceur d'émission

#### **Problème**

Lors du passage en émission, il faut activer les composants dans le bon ordre : d'abord l'accordeur d'antenne, puis l'amplificateur, enfin l'émetteur.

### Solution avec portes logiques

Utilisation de portes AND pour créer des délais logiques et assurer la séquence correcte. Chaque étage ne s'active que si l'étage précédent est prêt (signal OK) ET que le PTT est activé.

### 2. Détecteur de tonalité CTCSS

### **Application**

Un décodeur CTCSS utilise des portes XOR pour comparer la fréquence reçue avec une référence locale. Quand les signaux sont en phase, le XOR produit un niveau continu permettant l'ouverture du squelch.

# 3. Commutateur d'antenne logique

### **Fonctionnement**

Des portes logiques contrôlent des relais pour commuter entre plusieurs antennes selon la bande sélectionnée. Un encodeur binaire (3 bits) permet de sélectionner jusqu'à 8 antennes différentes.

# 4. Interface CAT (Computer Aided Transceiver)

### **Utilité**

Les portes logiques sont utilisées dans les interfaces RS-232 pour adapter les niveaux de tension entre l'ordinateur (±12V) et le transceiver (0-5V). Le circuit MAX232 contient des inverseurs et des amplificateurs de niveau.

# Points Clés à Retenir

- Les **portes logiques** réalisent physiquement les opérations booléennes

- Il existe deux normes de symboles (américaine et européenne)

- NAND et NOR sont des portes universelles

- Les familles logiques (TTL, CMOS, HC, LS) ont des caractéristiques différentes

- Le **74HC** est un excellent choix pour les projets amateurs

- Toujours consulter la **datasheet** avant utilisation

- Ne jamais oublier les condensateurs de découplage

- Respecter le **fan-out** et les niveaux logiques

73 de F4HXN - Prochaine fiche : Les systèmes de numération !

FICHE 4

# Les Systèmes de Numération

Octal, hexadécimal, BCD et autres systèmes pour représenter les nombres

# **Introduction aux Bases de Numération**

Un système de numération (ou base) est une méthode pour représenter des nombres. La base détermine combien de chiffres différents sont utilisés.

### Principe général :

Dans un système en base b, on utilise b chiffres différents (de 0 à b-1). Chaque position représente une puissance de la base.

**Exemple:** En base 10, on utilise 10 chiffres (0-9) et chaque position représente une puissance de 10 (unités, dizaines, centaines, etc.)

# Récapitulatif des bases courantes

| Base | Nom         | Chiffres<br>utilisés                     | Suffixe                 | Usage principal                          |

|------|-------------|------------------------------------------|-------------------------|------------------------------------------|

| 2    | Binaire     | 0, 1                                     | <sub>2</sub> ou 0b      | Électronique,<br>informatique            |

| 8    | Octal       | 0, 1,<br>2, 3,<br>4, 5,<br>6, 7          | 8 OU 00                 | Permissions<br>Unix, anciens<br>systèmes |

| 10   | Décimal     | 0, 1,<br>2, 3,<br>4, 5,<br>6, 7,<br>8, 9 | 10<br>(souvent<br>omis) | Usage courant                            |

| 16   | Hexadécimal | 0-9,<br>A-F                              | <sub>16</sub> ou 0x     | Adresses<br>mémoire,<br>couleurs         |

# **10** Le Système Octal (Base 8)

Le système octal utilise  $\mathbf{8}$  chiffres: 0, 1, 2, 3, 4, 5, 6, 7

# **Table 1** Avantage de l'octal :

Chaque chiffre octal correspond exactement à **3 bits** en binaire, ce qui simplifie grandement les conversions.

# **Correspondance Octal** $\leftrightarrow$ **Binaire**

| Octal | Binaire (3 bits) | Décimal |

|-------|------------------|---------|

| 0     | 000              | Θ       |

| 1     | 001              | 1       |

| 2     | 010              | 2       |

| 3     | 011              | 3       |

| 4     | 100              | 4       |

| 5     | 101              | 5       |

| 6     | 110              | 6       |

| 7     | 111              | 7       |

# **Conversion Binaire** $\rightarrow$ **Octal**

### Méthode rapide

Grouper les bits par 3 en partant de la droite, puis convertir chaque groupe :

Binaire : 110101011<sub>2</sub>

Grouper par 3 : **110 101 011**

$653 = 653_8$

110101011<sub>2</sub> = 653<sub>8</sub>

# **Applications de l'octal**

#### **Permissions Unix/Linux**

Les droits d'accès aux fichiers sont souvent exprimés en octal :

chmod 755 fichier.txt

- 7 (111) = lecture + écriture + exécution pour le propriétaire

- 5 (101) = lecture + exécution pour le groupe

- 5 (101) = lecture + exécution pour les autres

# Le Système Hexadécimal (Base 16)

Le système hexadécimal utilise 16 symboles :

0 1 2 3 4 5 6 7 8 9 A B C D E F

$$A = 10$$

$$B = 11$$

$$C = 12$$

$$D = 13$$

$$E = 14$$

$$F = 15$$

# **③** Avantage de l'hexadécimal:

Chaque chiffre hexadécimal correspond exactement à **4 bits** (un nibble), ce qui permet de représenter un octet (8 bits) avec seulement 2 chiffres hexa.

# **Table de Correspondance Complète (0-255)**

| Décimal | Hexadécimal | Binaire (8 bits) |

|---------|-------------|------------------|

| 0       | 00          | 0000000          |

| 15      | 0F          | 00001111         |

| 16      | 10          | 00010000         |

| 31      | 1F          | 00011111         |

| 32      | 20          | 00100000         |

| 127     | 7F          | 01111111         |

| 128     | 80          | 1000000          |

| 255     | FF          | 11111111         |

### **Conversion Binaire** $\leftrightarrow$ **Hexadécimal**

**Binaire** → **Hexa**: **Grouper** par 4

Binaire : 11010110101111<sub>2</sub>

Grouper par 4 : **0011 0101 1010 1111**

$3 5 A F = 35AF_{16}$

11010110101111<sub>2</sub>

35AF<sub>16</sub>

**Hexa** → **Binaire** : **Convertir** chaque chiffre

Hexadécimal : 2F8A<sub>16</sub>

2 = 0010 | F = 1111 | 8 = 1000 | A = 1010

00101111100010102

# **Applications de l'hexadécimal**

### Adresses mémoire

Les adresses en informatique sont exprimées en hexadécimal :

0x7FFF2AC4 0xDEADBEEF

Plus compact que le binaire et plus lisible!

### **Couleurs RGB**

Les couleurs web sont codées en hexadécimal (RR GG BB) :

**#FF0000** = Rouge pur

#**00FF00** = Vert pur

**#0076A5** = Bleu F4HXN!

### Adresses MAC en réseau

Les adresses MAC sont exprimées en hexa :

00:1A:2B:3C:4D:5E

Chaque paire représente un octet (8 bits)

# **Conversions Entre Bases**

### Méthode Générale : Base quelconque - Décimal

### **Formule**

Multiplier chaque chiffre par la puissance correspondante de la base :

Nombre =

$$d_{(n)} \times base^n + d_{(n-1)} \times base^{n-1}$$

+ ... +  $d_1 \times base^1 + d_0 \times base^0$

### Exemple 1 : 2A3<sub>16</sub> → Décimal

- 1 Identifier les chiffres : 2, A (=10), 3

- 2 Appliquer les puissances de 16 :

$$2\times16^{2} + 10\times16^{1} + 3\times16^{0}$$

3 Calculer:

$$2\times256 + 10\times16 + 3\times1 = 512 + 160 + 3 = 675_{10}$$

### Exemple 2 : 157<sub>8</sub> → Décimal

$$1 \times 8^{2} + 5 \times 8^{1} + 7 \times 8^{0} = 64 + 40 + 7 = 111_{10}$$

# **Décimal** → **Base quelconque**

### Méthode des divisions successives

Convertir 234<sub>10</sub> en hexadécimal :

- 234 ÷ 16 = 14 reste **10 (A)**  $\leftarrow$  chiffre de poids faible

- 2  $14 \div 16 = 0$  reste **14 (E)**  $\leftarrow$  chiffre de poids fort

Lire de bas en haut :

EA<sub>16</sub>

Vérification :  $14 \times 16 + 10 = 224 + 10 = 234 \checkmark$

# **Tableau de Conversion Rapide**

| Décimal | Binaire  | Octal | Hexadécimal |

|---------|----------|-------|-------------|

| Θ       | 0000     | 0     | Θ           |

| 1       | 0001     | 1     | 1           |

| 2       | 0010     | 2     | 2           |

| 8       | 1000     | 10    | 8           |

| 10      | 1010     | 12    | А           |

| 15      | 1111     | 17    | F           |

| 16      | 10000    | 20    | 10          |

| 32      | 100000   | 40    | 20          |

| 64      | 1000000  | 100   | 40          |

| 255     | 11111111 | 377   | FF          |

# Le Code BCD (Binary Coded Decimal)

Le **BCD** code chaque chiffre décimal sur 4 bits. C'est un compromis entre binaire pur et décimal.

# Principe:

Chaque chiffre décimal (0-9) est représenté par son équivalent binaire sur 4 bits.

Attention : Les valeurs 1010 à 1111 (10-15) ne sont jamais utilisées en BCD!

# **Table BCD**

| Décimal | BCD (4 bits) |

|---------|--------------|

| Θ       | 0000         |

| 1       | 0001         |

| 2       | 0010         |

| 3       | 0011         |

| 4       | 0100         |

| 5       | 0101         |

| 6       | 0110         |

| 7       | 0111         |

| 8       | 1000         |

| 9       | 1001         |

### **Exemple: Coder 147 en BCD**

Chaque chiffre séparément :

**1** → **0001**

**4** → **0100**

$\textbf{7} \ \rightarrow \ \textbf{0111}$

147<sub>10</sub> = 0001 0100 0111 (BCD)

### **⚠** Différence avec binaire pur :

$147_{10}$  en binaire = **10010011** (8 bits)

$147_{10}$  en BCD = **0001 0100 0111** (12 bits)

Le BCD utilise plus de bits mais simplifie l'affichage décimal!

# **Applications du BCD**

### **Afficheurs 7 segments**

Les décodeurs BCD vers 7 segments (comme le 7447) prennent directement une entrée BCD pour commander un afficheur.

### **Calculs financiers**

Le BCD évite les erreurs d'arrondi en virgule flottante. Utilisé dans les systèmes bancaires et les calculatrices.

### Afficheurs de fréquence

Les fréquencemètres et transceiveurs avec affichage numérique utilisent souvent du BCD pour commander les afficheurs LED ou LCD.

# **Le Code Gray**

Le **code Gray** (ou code binaire réfléchi) est un système où deux valeurs consécutives ne diffèrent que d'un seul bit.

### **Table 1 Order 1 Order 2 Order 2 Order 3 <b>Order 3 Order 3 <b>Order 3 Order 3 Order 3 Order 3 Order 3 Order 3 <b>Order 3 Order 3 Order 3 Order 3 <b>Order 3 Order 3 Order 3 <b>Order 3 Order 3 Order 3 Order 3 Order 3 <b>Order 3 O**

Élimine les erreurs de transition ! Quand un compteur passe de 3 à 4 en binaire, tous les bits changent (011  $\rightarrow$  100). En Gray, un seul bit change.

# **Table de Conversion (4 bits)**

| Décimal | Binaire | Code Gray | Bits changés |

|---------|---------|-----------|--------------|

| 0       | 0000    | 0000      | -            |

| 1       | 0001    | 0001      | 1            |

| 2       | 0010    | 0011      | 1            |

| 3       | 0011    | 0010      | 1            |

| 4       | 0100    | 0110      | 1            |

| 5       | 0101    | 0111      | 1            |

| 6       | 0110    | 0101      | 1            |

| 7       | 0111    | 0100      | 1            |

| 8       | 1000    | 1100      | 1            |

# **Applications du code Gray**

### Encodeurs rotatifs

Les encodeurs de position utilisent le code Gray pour éviter les lectures erronées lors des transitions.

### Tableaux de Karnaugh

Les lignes et colonnes des tableaux de Karnaugh (simplification logique) utilisent l'ordre Gray pour faciliter le regroupement des cases adjacentes.

### **Conversion A/N**

Certains convertisseurs analogique-numérique utilisent le Gray pour minimiser les erreurs pendant la conversion.

# Représentation des Nombres Signés

Pour représenter des nombres négatifs en binaire, plusieurs méthodes existent :

# 1. Signe et Valeur Absolue

Le bit de poids fort indique le signe (0 = positif, 1 = négatif).

#### Sur 8 bits:

- **0**0101010 = +42

- **1**0101010 = -42

Problème: Deux représentations du zéro (+0 et -0)!

# 2. Complément à 1

Inverser tous les bits pour obtenir le négatif.

### **Exemple:**

- +42 = 00101010

- -42 = 11010101 (tous les bits inversés)

Problème : Encore deux représentations du zéro !

# 3. Complément à 2 (méthode standard)

La méthode universellement utilisée en informatique!

### Procédure:

- 1. Prendre le binaire du nombre positif

- 2. Inverser tous les bits (complément à 1)

- 3. Ajouter 1

# Exemple : -42 en complément à 2 sur 8 bits

+42 en binaire : 00101010

2 Inverser tous les bits : 11010101

3 Ajouter 1 : 11010101 + 1 = **11010110**

-42 = **11010110** (complément à 2)

# Plages de valeurs

| Nombre de bits | Plage signée (complément à 2)                 |

|----------------|-----------------------------------------------|

| 8 bits         | -128 à +127                                   |

| 16 bits        | -32 768 à +32 767                             |

| 32 bits        | -2 147 483 648 à +2 147 483 647               |

| 64 bits        | -9 × 10 <sup>18</sup> à +9 × 10 <sup>18</sup> |

### Avantages du complément à 2 :

- Une seule représentation du zéro

- L'addition fonctionne de la même manière pour les positifs et négatifs

- Pas besoin de circuit séparé pour la soustraction

- Détection de dépassement simple

# Nombres à Virgule

# **Virgule Fixe**

Un nombre de bits est réservé pour la partie entière, le reste pour la partie décimale.

# Format 8.8 (8 bits entiers, 8 bits décimaux)

Le nombre 42.25 serait représenté :

# **Virgule Flottante (IEEE 754)**

Format utilisé par tous les processeurs modernes.

### Format 32 bits (simple précision) :

- **1** bit : signe (0 = positif, 1 = négatif)

- 8 bits : exposant (polarisé de 127)

- 23 bits : mantisse (partie fractionnaire)

```

Valeur = (-1)^{signe} \times 2^{(exposant-127)} \times (1 +

mantisse)

```

### **Valeurs spéciales**

- **Exposant = 0, Mantisse = 0** : Zéro (+0 ou -0)

- Exposant = 255, Mantisse = 0 : Infini (+ $\infty$  ou - $\infty$ )

- Exposant = 255, Mantisse  $\neq$  0 : NaN (Not a Number)

### **A** Erreurs d'arrondi :

Les nombres comme 0.1 ou 0.3 ne peuvent pas être représentés exactement en virgule flottante binaire! C'est pourquoi 0.1 + 0.2 ≠ 0.3 en informatique.

Utiliser le BCD pour les calculs financiers nécessitant une précision décimale exacte.

# Applications Pratiques

### **Programmation**

En C/C++:

### Fréquences radio

Affichage LCD d'un transceiver :

La fréquence 14.250.000 Hz peut être stockée :

• En binaire : pour les calculs internes

• En BCD : pour l'affichage direct

• En hexa : pour les commandes CAT

### **Graphisme**

Couleur 24 bits (True Color):

```

\#FF6347 = RGB(255, 99, 71) = Tomate

```

FF = Rouge (255), 63 = Vert (99), 47 = Bleu (71)

# Points Clés à Retenir

- Octal : 8 chiffres, grouper par 3 bits, permissions Unix

- Hexadécimal : 16 symboles (0-F), grouper par 4 bits, adresses mémoire

- BCD : Chaque chiffre décimal sur 4 bits, afficheurs

- Code Gray : Un seul bit change entre valeurs consécutives

- Complément à 2 : Méthode standard pour les nombres signés

- L'hexadécimal est le plus utilisé en électronique et informatique

- Bien distinguer binaire pur et BCD

- Le code Gray évite les erreurs de transition

73 de F4HXN - Prochaine fiche : Les tableaux de Karnaugh ! 📡

FICHE 5

# Les Tableaux de Karnaugh

Simplifiez vos circuits logiques avec une méthode graphique puissante

# Pourquoi Simplifier les Circuits?

En électronique numérique, une même fonction logique peut être réalisée de plusieurs façons différentes. La **simplification** permet de :

- Réduire le **nombre de portes logiques** nécessaires

- Diminuer le coût du circuit

- Réduire la consommation électrique

- Augmenter la vitesse (moins de portes = moins de délais)

- Améliorer la **fiabilité** (moins de composants = moins de pannes)

### **Exemple concret**

**Expression non simplifiée:**

$$F = A \cdot B \cdot C + A \cdot B \cdot \bar{C} + A \cdot \bar{B} \cdot C + \bar{A} \cdot B \cdot C$$

Nécessite : 4 portes AND à 3 entrées + 1 porte OR à 4 entrées + inverseurs = ~12 portes

**Expression simplifiée:**

$$F = A \cdot B + B \cdot C + A \cdot C$$

Nécessite : 3 portes AND à 2 entrées + 1 porte OR à 3 entrées = ~4 portes

Économie de 66% de composants!

# Méthodes de Simplification

# 1. Méthode Algébrique

Utilise les lois de l'algèbre de Boole pour simplifier les expressions.

### **Exemple:**

$$F = A \cdot B + A \cdot \overline{B}$$

$$F = A \cdot (B + \overline{B}) \text{ [factorisation]}$$

$$F = A \cdot 1 \text{ [B + \overline{B} = 1]}$$

$$F = A$$

Problème : Fastidieuse pour les expressions complexes, nécessite de l'expérience et de l'intuition. On peut facilement passer à côté de la meilleure simplification.

# 2. Tableau de Karnaugh (Méthode Graphique)

Méthode **systématique et visuelle** qui garantit une simplification optimale!

### Avantages :

- Méthode **visuelle** et intuitive

- Garantit une simplification optimale

- Fonctionne bien jusqu'à 4-5 variables

- Plus rapide que l'algèbre pour les circuits moyens

- Facile à vérifier

# Principe du Tableau de Karnaugh

Le tableau de Karnaugh est un tableau où :

- Chaque case représente une combinaison des variables d'entrée

- Les cases sont ordonnées selon le code Gray (un seul bit change entre cases adjacentes)

- On place dans chaque case la valeur de sortie (0 ou 1)

- On regroupe les cases adjacentes contenant des 1 par groupes de 2,

4, 8, etc.

- Chaque groupe donne un terme simplifié

### Principe clé :

Les cases adjacentes ne diffèrent que d'une seule variable. En les regroupant, on peut **éliminer** cette variable de l'expression!

**Exemple:**  $A \cdot B \cdot C + A \cdot B \cdot \overline{C} = A \cdot B \cdot (C + \overline{C}) = A \cdot B$

# **Tableau de Karnaugh à 2 Variables**

Pour 2 variables (A et B), le tableau a 4 cases ( $2^2 = 4$  combinaisons).

# Structure du tableau

|   | В   |     |

|---|-----|-----|

| А | 0   | 1   |

| 0 | Ā·Ē | Ā·B |

| 1 | Α·Ē | A·B |

### Exemple : $F = A \cdot B + \bar{A} \cdot B$

Étape 1 : Placer les 1 dans le tableau

|   |   | 3 |

|---|---|---|

| А | 0 | 1 |

| 0 | 0 | 1 |

| 1 | 0 | 1 |

**Étape 2 :** Regrouper les cases adjacentes contenant des 1

Les deux 1 sont verticalement adjacents  $\rightarrow$  on peut les regrouper

Étape 3 : Lire le groupe

Le groupe couvre A=0 et A=1, donc **A varie** (on l'élimine)

Le groupe est entièrement dans la colonne B=1, donc **B reste**

$$F = B$$

**Expression simplifiée : F = B**

# Tableau de Karnaugh à 3 Variables

Pour 3 variables (A, B, C), le tableau a 8 cases (23 = 8 combinaisons).

### **Structure du tableau (disposition Gray)**

|   | BC    |       |       |       |  |

|---|-------|-------|-------|-------|--|

| А | 00    | 01    | 11    | 10    |  |

| 0 | Ā·Ē·Ĉ | Ā·Ē·C | Ā·B·C | Ā·B·Ē |  |

| 1 | A·Ē·Ĉ | A·Ē·C | A·B·C | A⋅B⋅Ĉ |  |

Important: L'ordre des colonnes est 00, 01, 11, 10 (code Gray), pas l'ordre numérique! Un seul bit change entre cases adjacentes.

### Exemple complet : Simplifier $F(A,B,C) = \Sigma(1,3,5,7)$

Les mintermines 1, 3, 5, 7 correspondent aux combinaisons où F=1:

- 1 = 001 =  $\bar{A} \cdot \bar{B} \cdot C$

- $3 = 011 = \bar{A} \cdot B \cdot C$

- $5 = 101 = A \cdot \bar{B} \cdot C$

- $7 = 111 = A \cdot B \cdot C$

Étape 1 : Placer les 1 dans le tableau

|   | ВС |    |    |    |

|---|----|----|----|----|

| Α | 00 | 01 | 11 | 10 |

| 0 | 0  | 1  | 1  | 0  |

| 1 | 0  | 1  | 1  | 0  |

**Étape 2 :** Identifier les regroupements possibles

On observe que tous les 1 forment un grand groupe de 4 cases (2×2)

Étape 3 : Analyser le regroupement

- Le groupe couvre A=0 et A=1 → A varie, on l'élimine

- Le groupe couvre uniquement B=0,C=1 (01) et B=1,C=1 (11)  $\rightarrow$  C=1 reste

- B varie dans le groupe → B s'élimine

$$F = C$$

Résultat : F = C (au lieu de 4 termes !)

# Tableau de Karnaugh à 4 Variables

Pour 4 variables (A, B, C, D), le tableau a **16 cases** (2<sup>4</sup> = 16 combinaisons).

### Structure du tableau 4×4

|    | CD |    |    |    |

|----|----|----|----|----|

| АВ | 00 | 01 | 11 | 10 |

| 00 | 0  | 1  | 5  | 4  |

| 01 | 2  | 3  | 7  | 6  |

| 11 | 10 | 11 | 15 | 14 |

| 10 | 8  | 9  | 13 | 12 |

Les numéros dans les cases correspondent aux valeurs décimales des combinaisons

Exemple :  $F(A,B,C,D) = \Sigma(0,1,2,5,8,9,10)$

|    | CD |    |    |    |  |

|----|----|----|----|----|--|

| АВ | 00 | 01 | 11 | 10 |  |

| 00 | 1  | 1  | 1  | 0  |  |

| 01 | 1  | 0  | 0  | 0  |  |

| 11 | 0  | 0  | 0  | 0  |  |

| 10 | 1  | 1  | 0  | 1  |  |

#### Regroupements identifiés :

1 Groupe de 4 : cases 0, 1, 8, 9 (colonne CD=00 et CD=01)

$$\bar{A} \cdot \bar{B} \cdot \bar{D} + \bar{A} \cdot \bar{B} \cdot D + A \cdot \bar{B} \cdot \bar{D} + A \cdot \bar{B} \cdot D = \bar{B} \cdot \bar{D}$$

(C varie, A et C s'éliminent, mais attendez...)

En fait : CD=00 ou 01  $\rightarrow$   $\bar{D}$  et  $\bar{B}$   $\rightarrow$   $\bar{B} \cdot \bar{D}$

2 Groupe de 2 : cases 0, 2 (colonne AB=00 et 01, CD=00)

$\boldsymbol{\bar{A}\cdot\bar{C}\cdot\bar{D}}$

**3 Groupe de 2 :** cases 1, 5 (ligne AB=00, colonnes CD=01 et 11)

$\bar{A} \cdot \bar{B} \cdot D$

**Expression finale simplifiée:**

$$F = \bar{B} \cdot \bar{D} + \bar{A} \cdot \bar{C} \cdot \bar{D} + \bar{A} \cdot \bar{B} \cdot D$$

Note : Cette simplification peut varier selon les regroupements choisis. L'objectif est de minimiser le nombre de termes.

# Règles de Regroupement

### Règles à respecter :

- 1. Les groupes doivent contenir un **nombre de cases qui est une puissance de 2** : 1, 2, 4, 8, 16

- 2. Les groupes doivent être **rectangulaires** (pas de forme en L)

- 3. Les groupes doivent être aussi grands que possible

- 4. Chaque 1 doit être dans au moins un groupe

- 5. Les groupes peuvent **se chevaucher**

- 6. Les **bords opposés** du tableau sont adjacents (effet torique)

## **Cas des bords adjacents**

### Le tableau est "torique"

|    | CD |    |    |    |

|----|----|----|----|----|

| АВ | 00 | 01 | 11 | 10 |

| 00 | 1  | 0  | 0  | 1  |

| 01 | 0  | 0  | 0  | 0  |

| 11 | 0  | 0  | 0  | 0  |

| 10 | 1  | 0  | 0  | 1  |

Les 4 coins forment un groupe valide ! (gauche et droite sont adjacents)

$$F = \bar{B} \cdot \bar{D}$$

# Les Conditions Indifférentes (Don't Care)

Parfois, certaines combinaisons d'entrées ne se produisent jamais ou leur sortie n'a pas d'importance. On les note X ou d (don't care).

#### **Utilisation stratégique :**

On peut considérer les X comme des 0 ou des 1 selon ce qui simplifie le mieux le circuit!

### **Exemple: Afficheur BCD**

Un décodeur BCD n'utilise que les combinaisons 0-9 (1010 à 1111 sont invalides en BCD).

|    | CD |    |    |    |  |

|----|----|----|----|----|--|

| АВ | 00 | 01 | 11 | 10 |  |

| 00 | 0  | 1  | 1  | 0  |  |

| 01 | 0  | 1  | 1  | 0  |  |

| 11 | Х  | Х  | Х  | Х  |  |

| 10 | Х  | Х  | Х  | Х  |  |

**Stratégie :** On peut inclure certains X dans nos groupes pour les agrandir !

En considérant les X comme des 1, on peut former un **grand groupe de** 8 cases (colonnes 01 et 11) :

$$F = D$$

Simplification maximale grâce aux don't care!

### Méthode Pas à Pas

1 Remplir le tableau

Placer les 1, 0 et X (don't care) dans chaque case selon la table de vérité

2 Identifier les groupes de 1

Chercher les plus grands groupes possibles (8, 4, 2, 1) en incluant éventuellement des X

3 Vérifier la couverture

S'assurer que tous les 1 sont dans au moins un groupe

4 Écrire les termes

Pour chaque groupe, écrire le produit des variables qui ne changent pas dans le groupe

#### **Combiner avec OR**

L'expression finale est la somme (OR) de tous les termes trouvés

# **Application : Contrôleur de Relais Radio**

#### Cahier des charges

Un relais amateur s'active SI:

- P : PTT activé (1=appuyé, 0=relâché)

- T : Tonalité CTCSS correcte (1=OK, 0=KO)

- S : Signal suffisant (1=bon, 0=faible)

- B : Batterie OK (1=OK, 0=faible)

#### Règles:

- Le relais s'active si PTT ET CTCSS ET Signal sont OK

- Si batterie faible, le relais ne s'active que si signal très fort (à définir)

- Certaines combinaisons impossibles (ex: PTT sans signal)

### Table de vérité simplifiée

| Р | т | S | В | Relais (F) |

|---|---|---|---|------------|

| 0 | 0 | 0 | 0 | 0          |

| 1 | 1 | 1 | 1 | 1          |

| 1 | 1 | 1 | 0 | 0          |

| 1 | 0 | 1 | 1 | 0          |

|   |   |   |   |            |

Après simplification par Karnaugh :

$$F = P \cdot T \cdot S \cdot B + autres termes...$$

Le circuit final nécessite moins de portes grâce à la simplification !

# **Comparaison des Méthodes**

| Critère                | Algèbre de<br>Boole     | Karnaugh                     |

|------------------------|-------------------------|------------------------------|

| Nombre de<br>variables | Illimité                | Pratique jusqu'à 4-5         |

| Garantie d'optimum     | Non                     | Oui                          |

| Facilité d'utilisation | Nécessite<br>expérience | Méthodique et visuel         |

| Rapidité               | Variable                | Rapide pour 2-4<br>variables |

| Don't care             | Difficile à gérer       | Facile à intégrer            |

| Automatisation         | Difficile               | Facile à programmer          |

### **®** Recommandation :

- 2 à 4 variables : Utiliser Karnaugh (rapide et optimal)

- 5-6 variables : Karnaugh possible mais fastidieux

- 7+ variables: Utiliser des logiciels (Quine-McCluskey, outils CAO)

### Points Clés à Retenir

- Les tableaux de Karnaugh permettent une **simplification** visuelle et systématique

- L'ordre des cases suit le **code Gray** (un seul bit change)

- Les groupes doivent être de taille 2n (1, 2, 4, 8, 16...)

- Toujours former les **groupes les plus grands** possibles

- Les **bords opposés** du tableau sont adjacents

- Les don't care (X) peuvent être 0 ou 1 selon ce qui simplifie le mieux

- Chaque groupe élimine les variables qui varient à l'intérieur

- Méthode **optimale** pour 2 à 4 variables

73 de F4HXN - Prochaine fiche : Les circuits combinatoires ! 📡

FICHE 6

# Les Circuits Combinatoires

Des additionneurs aux multiplexeurs : les briques de base de l'informatique

# **Qu'est-ce qu'un Circuit Combinatoire?**

Un circuit combinatoire est un circuit logique dont les sorties dépendent uniquement des valeurs actuelles des entrées, sans mémoire du passé.

#### **Caractéristiques :**

- Pas de mémoire : aucun état interne conservé

- Pas de boucle de rétroaction

- Réponse instantanée (à la vitesse des portes)

- Peut être décrit par une table de vérité ou une fonction logique

#### **Circuit Combinatoire**

Sortie = f(Entrées actuelles)

#### **Exemples:**

- Additionneur

- Multiplexeur

- Décodeur

- Comparateur

### **Ö** Circuit Séquentiel

Sortie = f(Entrées, État précédent)

#### **Exemples:**

- Bascules

- Compteurs

- Registres

- Mémoires

### **Les Additionneurs**

### **Demi-Additionneur (Half Adder)**

Le demi-additionneur additionne deux bits sans retenue d'entrée.

| Α | В | Somme (S) | Retenue (C) |

|---|---|-----------|-------------|

| 0 | 0 | Θ         | Θ           |

| 0 | 1 | 1         | Θ           |

| 1 | 0 | 1         | Θ           |

| 1 | 1 | Θ         | 1           |

$$S = A \oplus B (XOR)$$

$C = A \cdot B (AND)$

#### Réalisation

Nécessite : 1 porte XOR + 1 porte AND

## **Additionneur Complet (Full Adder)**

L'**additionneur complet** additionne deux bits PLUS une retenue d'entrée (Cin).

| Α | В | Cin | Somme (S) | Retenue (Cout) |

|---|---|-----|-----------|----------------|

| Θ | Θ | Θ   | Θ         | Θ              |

| 0 | 0 | 1   | 1         | 0              |

| 0 | 1 | Θ   | 1         | 0              |

| 0 | 1 | 1   | 0         | 1              |

| 1 | 0 | 0   | 1         | 0              |

| 1 | 0 | 1   | 0         | 1              |

| 1 | 1 | 0   | 0         | 1              |

| 1 | 1 | 1   | 1         | 1              |

$$S = A \oplus B \oplus Cin$$

$$Cout = (A \cdot B) + (Cin \cdot (A \oplus B))$$

## **Circuits intégrés**

7483 Additionneur 4 bits 74283 Additionneur 4 bits rapide

### **Additionneur N bits**

#### Addition de nombres multi-bits

Pour additionner des nombres de N bits, on cascade N additionneurs complets :

- Le bit de poids faible utilise un additionneur complet avec Cin = 0

- 2 Chaque Cout devient le Cin de l'étage suivant

- 3 Le Cout final indique un dépassement de capacité

#### Exemple: 5 + 3 sur 4 bits

```

0101 (5)

+ 0011 (3)

-----

1000 (8)

```

### Le Soustracteur

La soustraction peut être réalisée en utilisant le complément à 2 :

#### Astuce :

A - B = A + (-B) = A + (complément à 2 de B)

On peut donc réutiliser un additionneur!

#### Réalisation d'un soustracteur

- Inverser tous les bits de B (avec des portes XOR)

- Ajouter 1 en mettant Cin = 1

- Utiliser un additionneur pour  $A + \bar{B} + 1$

Avantage : Le même circuit peut faire addition ET soustraction avec un signal de contrôle!

# **Le Comparateur de Magnitude**

Le **comparateur** compare deux nombres binaires et indique si A > B, A = B, ou A < B.

### **Comparateur 1 bit**

| Α | В | A > B | A = B | A < B |

|---|---|-------|-------|-------|

| Θ | 0 | Θ     | 1     | Θ     |

| 0 | 1 | Θ     | Θ     | 1     |

| 1 | Θ | 1     | 0     | 0     |

| 1 | 1 | 0     | 1     | 0     |

$$A > B = A \cdot \bar{B}$$

$A = B = A \odot B (XNOR)$

$A < B = \bar{A} \cdot B$

### **Circuits intégrés**

7485 Comparateur 4 bits

### **Application radio**

Comparer la valeur du ROS avec un seuil de sécurité. Si ROS > seuil, couper l'émetteur.

# Le Multiplexeur (MUX)

Le multiplexeur sélectionne une entrée parmi N et la route vers la sortie, selon un code de sélection.

#### Name :

Un MUX à N entrées nécessite log<sub>2</sub>(N) lignes de sélection.

- MUX 2:1 → 1 ligne de sélection

- MUX 4:1 → 2 lignes de sélection

- MUX 8:1 → 3 lignes de sélection

### **Multiplexeur 2:1**

| S (Sélection) | Sortie Y                  |

|---------------|---------------------------|

| Θ             | I₀ (entrée 0)             |

| 1             | I <sub>1</sub> (entrée 1) |

$$Y = \bar{S} \cdot I_0 + S \cdot I_1$$

# **Multiplexeur 4:1**

| S <sub>1</sub> | So | Sortie Y       |

|----------------|----|----------------|

| 0              | Θ  | Ι <sub>Θ</sub> |

| 0              | 1  | I <sub>1</sub> |

| 1              | 0  | I <sub>2</sub> |

| 1              | 1  | Ι <sub>3</sub> |

#### **Applications**

#### 1. Sélection de source audio

Choisir entre microphone local, liaison téléphonique, ou réception radio

#### 2. Commutation d'antennes

Sélectionner une antenne parmi plusieurs selon la bande

#### 3. Transmission série

Convertir des données parallèles en série (un bit à la fois)

#### 4. Implémentation de fonctions logiques

Un MUX peut réaliser n'importe quelle fonction logique!

# Le Démultiplexeur (DEMUX)

Le **démultiplexeur** fait l'opération inverse : il route une entrée vers l'une des N sorties.

#### Principe:

Un DEMUX 1:N utilise log<sub>2</sub>(N) lignes de sélection pour choisir la sortie active.

### Démultiplexeur 1:4

| S <sub>1</sub> | So | Yo | <b>Y</b> <sub>1</sub> | <b>Y</b> <sub>2</sub> | Υ <sub>3</sub> |

|----------------|----|----|-----------------------|-----------------------|----------------|

| Θ              | Θ  | D  | Θ                     | Θ                     | 0              |

| 0              | 1  | 0  | D                     | 0                     | Θ              |

| 1              | Θ  | 0  | 0                     | D                     | 0              |

| 1              | 1  | 0  | 0                     | 0                     | D              |

### **Circuits intégrés**

**74139** Dual DEMUX 1:4 **74138** DEMUX 1:8

### **Application : Adressage mémoire**

Un DEMUX permet de sélectionner une case mémoire parmi plusieurs selon son adresse binaire.

## **Encodeur et Décodeur**

### **Encodeur (Encoder)**

Un **encodeur** convertit 2<sup>N</sup> entrées en un code binaire de N bits.

### **Encodeur 8:3 (Octal vers Binaire)**

| Entrée active  | <b>A</b> <sub>2</sub> | Aı | Ao | Code |

|----------------|-----------------------|----|----|------|

| Ιo             | 0                     | 0  | 0  | 0    |

| Ιı             | 0                     | 0  | 1  | 1    |

| I <sub>2</sub> | 0                     | 1  | 0  | 2    |

| Ι <sub>3</sub> | 0                     | 1  | 1  | 3    |

| I 4            | 1                     | 0  | 0  | 4    |

| Ι <sub>5</sub> | 1                     | 0  | 1  | 5    |

| Ι <sub>6</sub> | 1                     | 1  | 0  | 6    |

| I <sub>7</sub> | 1                     | 1  | 1  | 7    |

74148 Encodeur prioritaire 8:3

74147

Encodeur décimal vers

**BCD**

### **Décodeur (Decoder)**

Un **décodeur** fait l'opération inverse : convertit N bits en 2<sup>N</sup> sorties (une seule active).

#### **Décodeur 3:8 (Binaire vers Octal)**

Si l'entrée est **101** (5), seule la sortie  $Y_5$  est active (1), toutes les autres sont à 0.

### **Circuits intégrés**

74138

Décodeur 3:8

7442

Décodeur BCD vers décimal

### **Applications**

- Sélection de périphériques : Activer un composant selon son adresse

- Affichage : Piloter des LEDs ou segments

- Distribution de signaux : Router un signal vers une destination

# **Décodeur 7 Segments**

Un **décodeur 7 segments** convertit un code BCD (0-9) en signaux pour piloter un afficheur 7 segments.

### Structure d'un afficheur 7 segments :

7 segments (a, b, c, d, e, f, g) disposés en forme de "8":

aaaa f b f b gggg e c e c

### **Exemple: Afficher le chiffre "5"**

Segments actifs : a, f, g, c, d

#### # #### # ####

### **Circuits intégrés**

7447 Décodeur BCD vers 7 seg. (anode commune)

7448

Décodeur BCD vers 7 seg. (cathode commune)

### **Application radio**

Afficher la fréquence, le canal, le niveau S-meter, ou le numéro de mémoire sur un transceiver.

# L'ALU (Unité Arithmétique et Logique)

L'**ALU** est le cœur de tout processeur. Elle réalise des opérations arithmétiques ET logiques selon un code de commande.

#### **©** Fonctions typiques d'une ALU :

- Arithmétiques : Addition, Soustraction, Incrémentation,

Décrémentation

- Logiques : AND, OR, XOR, NOT

- Comparaison : Égalité, Supérieur, Inférieur

- Décalages : Shift left, Shift right

### **Structure d'une ALU simple**

### **Composants principaux**

- 1 Additionneur/Soustracteur pour les opérations arithmétiques

- **Portes logiques** (AND, OR, XOR) pour les opérations logiques

- Multiplexeur pour sélectionner le résultat selon l'opération

- 4 Flags : Carry (retenue), Zero (résultat nul), Negative (signe), Overflow

### **Table des opérations (exemple 4 bits)**

| Code Op | Opération | Résultat |

|---------|-----------|----------|

| 000     | A AND B   | А·В      |

| 001     | A OR B    | A + B    |

| 010     | A XOR B   | A ⊕ B    |

| 011     | NOT A     | Ā        |

| 100     | ADD       | A + B    |

| 101     | SUB       | A - B    |

| 110     | INC       | A + 1    |

| 111     | DEC       | A - 1    |

### **Circuits intégrés**

74181 ALU 4 bits (classique!) 74381 ALU 4 bits rapide

#### **Note historique :**

Le 74181 fut l'une des premières ALU intégrées (1970). Elle peut réaliser 16 opérations logiques et 16 opérations arithmétiques ! C'est un composant légendaire de l'histoire de l'informatique.

# Projet Pratique : Additionneur 4 bits

#### **Objectif**

Construire un additionneur 4 bits avec affichage 7 segments du résultat.

#### Matériel nécessaire

- 4× Circuits intégrés 7483 (additionneur 4 bits) ou équivalent

- 1× Circuit 7447 (décodeur BCD vers 7 segments)

- 1× Afficheur 7 segments

- 8× Interrupteurs DIP (pour A et B)

- 5× LEDs (pour afficher le résultat en binaire)

- Résistances 330Ω

- Alimentation 5V

- Plaque d'essai

### 1 Entrées

Connecter 4 interrupteurs pour A  $(A_3A_2A_1A_0)$  et 4 pour B  $(B_3B_2B_1B_0)$

# 2 Addition

Utiliser le 7483 pour additionner A + B. Connecter Cin à 0.

#### Affichage binaire

Connecter 5 LEDs aux sorties (S<sub>3</sub>S<sub>2</sub>S<sub>1</sub>S<sub>0</sub> + Cout) pour voir le résultat en binaire

#### Affichage décimal

Connecter les 4 bits de somme au 7447, puis au 7-segments pour affichage 0-9

#### **Test**

Tester plusieurs additions : 5+3=8, 7+6=13 (affichera 3 en décimal + Cout=1)

#### **Extension possible:**

Ajouter un inverseur et un MUX pour créer un additionneur/soustracteur sélectionnable!

# **Applications en Radio Amateur**

### Synthétiseur de fréquence

Les additionneurs calculent les fréquences intermédiaires dans les PLL.

#### S-Meter numérique

Comparateurs pour convertir le niveau du signal en indication visuelle par paliers.

#### Sélecteur de mémoire

Encodeur pour convertir les touches en code binaire de canal.

### Affichage de fréquence

Décodeurs BCD vers 7-segments pour afficher les MHz, kHz.

#### **Commutateur d'antenne**

Décodeur 3:8 pour sélectionner 1 parmi 8 antennes selon la bande.

## **Contrôle de gain**

MUX pour sélectionner différents niveaux d'atténuation RF.

## **Résumé des Circuits Combinatoires**

| Circuit                 | Fonction                            | CI<br>typique |

|-------------------------|-------------------------------------|---------------|

| Demi-additionneur       | A + B (2 bits)                      | -             |

| Additionneur<br>complet | A + B + Cin                         | 7483          |

| Soustracteur            | A - B                               | -             |

| Comparateur             | A ? B                               | 7485          |

| Multiplexeur            | Sélection N:1                       | 74151         |

| Démultiplexeur          | Distribution<br>1:N                 | 74138         |

| Encodeur                | $2^N \rightarrow N \text{ bits}$    | 74148         |

| Décodeur                | N bits $\rightarrow$ 2 <sup>N</sup> | 74138         |

| Décodeur 7-seg          | BCD → 7<br>segments                 | 7447          |

| ALU                     | Arith. +<br>Logique                 | 74181         |

## Points Clés à Retenir

- Les circuits combinatoires n'ont pas de mémoire

- L'additionneur complet est la brique de base de l'arithmétique

- La soustraction utilise le complément à 2

- Le multiplexeur sélectionne une entrée parmi N

- Le **décodeur** active une sortie parmi N

- Les **encodeurs** convertissent 2<sup>N</sup> → N bits

- L'ALU combine arithmétique et logique

- Ces circuits sont les **briques de base** de tout processeur

73 de F4HXN - Prochaine fiche : Les circuits séquentiels ! 📡

FICHE 7

Bascules, registres, compteurs et mémoires : les circuits qui se souviennent

## Circuit Séquentiel vs Combinatoire

Un circuit séquentiel possède une mémoire : sa sortie dépend non seulement des entrées actuelles, mais aussi de l'état précédent.

#### **Circuit Combinatoire**

Sortie = f(Entrées)

- Pas de mémoire

- Réponse immédiate

- Pas d'horloge

- Table de vérité fixe

#### **Circuit Séquentiel**

#### Sortie = f(Entrées, État)

- Possède une mémoire

- Évolution dans le temps

- Souvent synchronisé par horloge

- Diagramme d'états

#### 🔑 Élément clé :

La **boucle de rétroaction** permet au circuit de mémoriser son état. La sortie est réinjectée à l'entrée, créant ainsi une mémoire.

## Les Bascules (Flip-Flops)

Une **bascule** est l'élément de mémoire de base. Elle peut stocker **1 bit** d'information.

## **Bascule RS (Set-Reset)**

La bascule RS est la plus simple. Elle a deux entrées : S (Set) et R (Reset).

| S | R | Q (sortie) | Q | Action           |

|---|---|------------|---|------------------|

| 0 | Θ | Q          | Q | Maintien         |

| 1 | Θ | 1          | Θ | Set (mise à 1)   |

| 0 | 1 | 0          | 1 | Reset (mise à 0) |

| 1 | 1 | Х          | X | Interdit !       |

#### **État interdit :**

S=1 et R=1 simultanément créent un état instable. Cette combinaison doit être évitée!

#### Réalisation avec portes NOR

Deux portes NOR avec rétroaction croisée forment une bascule RS.

$$Q = \bar{S} + R \cdot Q$$

(simplifiée)

$\bar{Q} = \bar{R} + S \cdot \bar{Q}$

## **Bascule D (Data)**

La bascule D capture la valeur de l'entrée D au moment du front d'horloge.

| CLK    | D | Q (après CLK) | Action      |

|--------|---|---------------|-------------|

| 1      | Θ | Θ             | Copie D → Q |

| 1      | 1 | 1             | Copie D → Q |

| 0 ou 1 | Х | Q             | Maintien    |

## **a** Avantage:

Pas d'état interdit! La bascule D élimine le problème de la RS. Elle est la plus utilisée dans les circuits modernes.

7474

Dual D Flip-Flop

#### **Application radio**

Synchroniser des signaux de commande avec une horloge système pour éviter les états transitoires indésirables.

## **Bascule JK**

La bascule JK est une amélioration de la RS qui élimine l'état interdit.

| J | K | Q (après CLK) | Action           |

|---|---|---------------|------------------|

| Θ | Θ | Q             | Maintien         |

| 0 | 1 | 0             | Reset            |

| 1 | Θ | 1             | Set              |

| 1 | 1 | Q             | Toggle (bascule) |

## → Caractéristique unique :

Quand J=K=1, la bascule **inverse** son état (toggle). C'est très utile pour créer des compteurs !

7476 Dual JK Flip-Flop

## **Bascule T (Toggle)**

La bascule T est une simplification de la JK. Elle a une seule entrée T.

| т | Q (après CLK) | Action           |

|---|---------------|------------------|

| 0 | Q             | Maintien         |

| 1 | Q             | Toggle (inverse) |

#### **Application typique**

Division de fréquence par 2. À chaque front d'horloge avec T=1, la sortie change d'état.

**Exemple :** Horloge 1 MHz → Sortie 500 kHz

## Synchrone vs Asynchrone

#### **Bascule Asynchrone**

Les entrées S et R agissent **immédiatement**, sans attendre l'horloge.

Usage: Initialisation, remise à zéro rapide

#### **Bascule Synchrone**

Les changements se font uniquement sur les fronts d'horloge.

Usage: Circuits numériques synchronisés

#### **©** Front d'horloge :

- Front montant (1): Transition de 0 vers 1

- Front descendant (↓): Transition de 1 vers 0

La plupart des circuits modernes utilisent le front montant.

## **Les Registres**

Un **registre** est un ensemble de bascules (généralement D) permettant de stocker plusieurs bits.

## Registre Parallèle

Toutes les bascules sont chargées **simultanément** sur le même front d'horloge.

#### **Registre 8 bits**

8 bascules D en parallèle stockent un octet complet.

Application : Mémoriser temporairement une donnée pendant un traitement.

74173

Registre 4 bits

74374

Registre 8 bits avec sortie 3 états

## Registre à Décalage (Shift Register)

Les bits se déplacent d'une position à chaque front d'horloge.

#### Exemple : Décalage vers la droite

#### **6** Applications des registres à décalage :

- **Délai numérique** (retard de N bits)

- Génération de séquences

- Multiplication/division par 2 (décalage = × ou ÷ 2)

74164 Registre à décalage 8 bits (série → parallèle) 74165

Registre à décalage 8 bits (parallèle → série) 74595 Registre à décalage 8 bits avec sortie tampon

#### **Application: Transmission série**

Les données de commande CAT vers le transceiver sont envoyées en série. Un registre à décalage convertit les 8 bits parallèles du microcontrôleur en flux série.

## **Les Compteurs**

Un compteur est un circuit séquentiel qui parcourt une séquence d'états à chaque impulsion d'horloge.

#### **Compteur Asynchrone (Ripple Counter)**

Chaque bascule est déclenchée par la sortie de la bascule précédente. L'horloge se "propage" en cascade.

#### **Compteur 4 bits asynchrone (modulo 16)**

```

Compte : 0000 \rightarrow 0001 \rightarrow 0010 \rightarrow 0011 \rightarrow ... \rightarrow 1111 \rightarrow 0000

(0)

(1) (2)

(3)

(15)

(0)

```

#### **A** Problème :

Délai de propagation cumulatif. À haute fréquence, des états transitoires indésirables peuvent apparaître.

## **Compteur Synchrone**

Toutes les bascules reçoivent la même horloge. Pas de délai cumulatif!

#### Avantages :

- Pas d'états transitoires (glitches)

- Fonctionne à haute fréquence

- Plus prévisible

7490 Compteur décade (0-9) 7493 Compteur binaire 4 bits

74161 Compteur synchrone 4 bits 74193 Compteur/décompteur

BCD synchrone

## **Types de Compteurs**

#### **Compteur UP**

Compte de manière croissante

$$0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow 4 \dots$$

## **Compteur DOWN**

Compte de manière décroissante

$$\dots 4 \ \rightarrow \ 3 \ \rightarrow \ 2 \ \rightarrow \ 1 \ \rightarrow \ 0$$

## **Compteur UP/DOWN**

Bidirectionnel selon un signal de contrôle

Signal DIR = montant ou descendant

### **Compteur Modulo N**

Compte de 0 à N-1 puis revient à 0

Exemple: modulo 10 = 0-9

### Application : Diviseur de fréquence

Un compteur modulo N divise la fréquence d'entrée par N.

**Exemple :** Compteur modulo 100 avec horloge 10 MHz  $\rightarrow$  sortie 100 kHz

Utilisé dans les synthétiseurs de fréquence (PLL) des transceivers.

#### **Projet: Compteur décimal avec affichage**

- 1 Utiliser un 7490 (compteur décade 0-9)

- 2 Connecter un 7447 (décodeur BCD vers 7 segments)

- 3 Afficher sur un afficheur 7 segments

- 4 Ajouter un bouton poussoir pour incrémenter

Résultat : Compteur manuel de 0 à 9 !

## Les Mémoires

Une **mémoire** est un circuit capable de stocker une grande quantité d'informations binaires.

## Organisation d'une mémoire

#### Paramètres clés :

- Capacité : Nombre de bits stockés (ex: 1 Ko = 8192 bits)

- Organisation : Nombre de mots × largeur (ex: 1024×8)

- Bus d'adresse : N bits → 2<sup>N</sup> adresses

- Bus de données : Largeur d'un mot (8, 16, 32 bits...)

#### **Exemple: Mémoire 1K×8**

- Capacité : 1024 mots de 8 bits = 8192 bits = 1 Ko

- Bus d'adresse : 10 bits ( $2^{10} = 1024$  adresses)

- Bus de données : 8 bits

## **RAM (Random Access Memory)**

Mémoire **volatile** : perd son contenu à la coupure de l'alimentation.

#### **SRAM (Static RAM)**

Utilise des bascules

- **Très rapide**

- V Pas de rafraîchissement

- X Plus coûteuse

- X Moins dense

Usage: Mémoire cache

### **DRAM (Dynamic RAM)**

Utilise des condensateurs

- V Haute densité

- Moins coûteuse

- X Nécessite rafraîchissement

- X Plus lente

Usage: Mémoire principale

6264

SRAM 8K×8

62256

SRAM 32K×8

## **ROM (Read-Only Memory)**

Mémoire non volatile : conserve les données sans alimentation.

#### **ROM (Mask ROM)**

Programmée en usine

Non modifiable. Coût élevé pour faibles volumes.

#### **PROM**

Programmable une fois

Fusibles "grillés". Ancienne technologie.

#### **EPROM**

#### Effaçable aux UV

Fenêtre en quartz. Effacement 15-20 min.

#### **EEPROM**

Effaçable électriquement

Effacement octet par octet. Lente en écriture.

#### **Flash**

**EEPROM** par blocs

Rapide, haute densité. Technologie moderne.

2764 EPROM 8K×8 27C256 EPROM 32K×8 28C256

EEPROM 32K×8

#### Mémoires dans un transceiver

• ROM/Flash : Firmware du transceiver

• **EEPROM** : Canaux mémoire, configuration

• RAM: Buffer audio, traitement DSP

## Signaux de contrôle

#### 🔀 Signaux typiques d'une mémoire :

• A0-An: Bus d'adresse

• D0-Dm : Bus de données (bidirectionnel)

• CS (Chip Select) : Sélection du circuit

• OE (Output Enable) : Activation des sorties

• WE (Write Enable) : Autorisation d'écriture

#### Lecture d'une mémoire

1 Placer l'adresse sur le bus A0-An

2 Activer CS (Chip Select) = 0

3 Activer OE (Output Enable) = 0

4 Attendre le temps d'accès

5 Lire les données sur le bus D0-Dm

## **Temps Caractéristiques**

#### **Taramètres temporels importants :**

#### Pour les bascules :

- Setup time (tsu) : Temps minimum avant le front d'horloge où l'entrée doit être stable

- Hold time (th): Temps minimum après le front où l'entrée doit rester stable

- Propagation delay (tpd) : Délai entre front d'horloge et changement de sortie

#### Pour les mémoires :

- Access time (tacc) : Temps entre adresse valide et données valides

- Cycle time (tcyc) : Temps minimum entre deux accès

- Write time (twr) : Durée d'impulsion d'écriture nécessaire

#### **Important**:

Le non-respect des temps setup et hold peut causer des métastabilités : état indéterminé de la bascule entre 0 et 1. Cela peut bloquer tout le système!

## • Projet Pratique : Chenillard LED

#### **Objectif**

Créer un effet de chenillard avec 8 LEDs qui s'allument séquentiellement.

#### **Matériel**

- 1× Circuit 74164 (registre à décalage 8 bits)

- 1× Circuit 555 (générateur d'horloge) ou Arduino

- 8× LEDs + résistances 330Ω

- 1× Résistance 10k $\Omega$ , 1× condensateur 10 $\mu$ F (pour 555)

- Alimentation 5V

## 1 Générateur d'horloge

Utiliser un 555 en mode astable pour générer une horloge ~1 Hz

## 2 Registre à décalage

Connecter le 74164. L'entrée série A et B = 1

## 3 LEDs

Connecter 8 LEDs (+ résistances) aux sorties Q0-Q7

#### **Boucle**

Pour faire boucler : connecter Q7 à l'entrée série (inversée avec un NOT)

#### Test

Les LEDs s'allument l'une après l'autre en continu!

#### **Wariantes**:

- Changer la vitesse (ajuster R et C du 555)

- Faire un aller-retour (compteur UP/DOWN)

- Plusieurs patterns avec un multiplexeur

## **Applications Radio Amateur**

#### Mémoires de fréquence

EEPROM pour sauvegarder canaux, CTCSS, modes

#### **Buffer DSP**

RAM rapide pour traitement audio numérique

## Affichage de fréquence

Registres pour maintenir l'affichage stable

## **Timer/Watchdog**

Compteur pour temporisation (TOT, squelch tail)

## **Contrôle de gain**

Registre à décalage pour CAG numérique

## Synthétiseur PLL

Compteurs programmables pour division de fréquence

## Points Clés à Retenir

- Les circuits séquentiels possèdent une mémoire

- Les **bascules** sont les éléments de mémoire de base (1 bit)

- La bascule **D** est la plus utilisée (pas d'état interdit)